Generating Random Data with the OSVVM Randomization Library

In this tutorial, we will discuss the most useful randomization functions supported by the OSVVM library.

In this tutorial, we will discuss the most useful randomization functions supported by the OSVVM library.

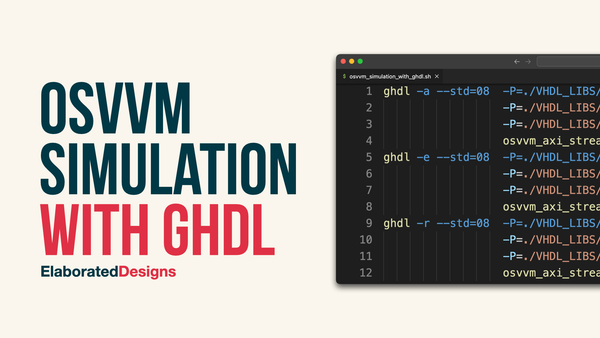

In this post, we will run a minimal OSVVM test bench with the free and open-source simulator GHDL.

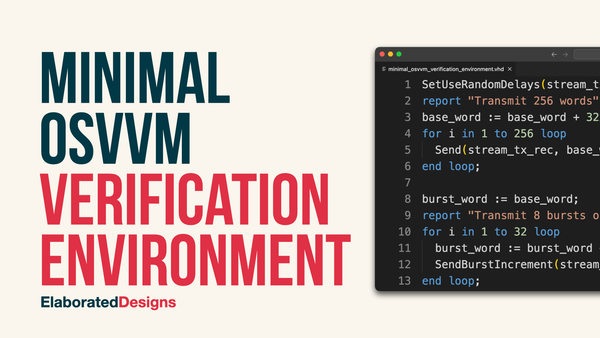

In this post we create a minimal, single-file verification environment using the OSVVM AXI-Stream Transmitter Verification Component.

In this post we compile the OSVVM libraries and run one of the built-in tests. We then discuss the architecture of an OSVVM testbench.

In this post we will generate a bitstream in Vivado using the Non-Project Mode.

In this post we discuss the Vivado Use Models (Project vs Non-Project Mode) and create a design in Project Mode.

In this post we will discuss the main components of the Vitis AI framework.

In this post we will discuss the overall Power Design process when using AMD FPGAs.

In this post we discuss the 10 elements needed for setting up a professional FPGA development environment, including specific choices for each category.

In this post we create and run a ‘Hello World’ program on the Zynq 7000 SoC using the Vitis Unified IDE.

In this post we will set up a minimal testbench to generate data using an AXI4-Stream Master Bus Functional Model from the UVVM Light library.